超大規(guī)模集成電路設(shè)計方法學(xué)導(dǎo)論

集成電路(IC)是現(xiàn)代電子技術(shù)的核心,而超大規(guī)模集成電路(VLSI)的設(shè)計方法學(xué)則是實現(xiàn)復(fù)雜功能芯片的關(guān)鍵。隨著技術(shù)進步,VLSI設(shè)計已從傳統(tǒng)的手工布局演變?yōu)楦叨茸詣踊牧鞒蹋w從系統(tǒng)級設(shè)計到物理實現(xiàn)的多個階段。本文簡要介紹VLSI設(shè)計方法學(xué)的基本概念、主要流程和未來趨勢。

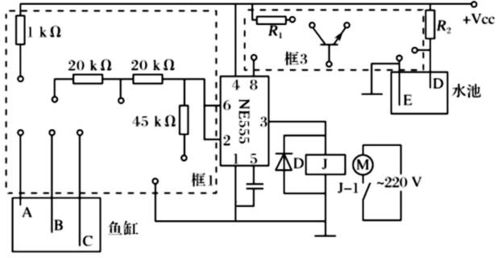

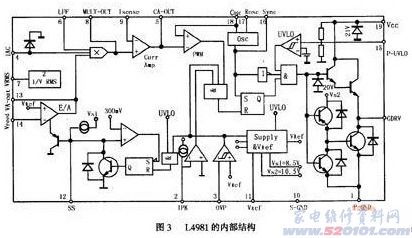

VLSI設(shè)計方法學(xué)涉及多個層次,包括系統(tǒng)級設(shè)計、架構(gòu)設(shè)計、邏輯設(shè)計、電路設(shè)計和物理設(shè)計。在系統(tǒng)級,設(shè)計師定義芯片的整體功能和性能指標(biāo),使用硬件描述語言(如Verilog或VHDL)進行建模。架構(gòu)設(shè)計則優(yōu)化數(shù)據(jù)路徑和控制單元,以提高吞吐量和能效。邏輯設(shè)計階段將功能轉(zhuǎn)換為門級網(wǎng)表,而電路設(shè)計關(guān)注晶體管級實現(xiàn),確保時序和功耗要求。物理設(shè)計涉及布局和布線,生成最終的掩模版圖,用于芯片制造。

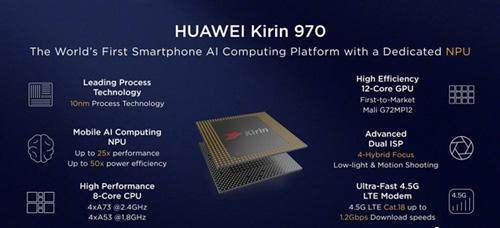

現(xiàn)代VLSI設(shè)計強調(diào)自動化工具的使用,如電子設(shè)計自動化(EDA)軟件,這些工具支持仿真、綜合和驗證,減少人為錯誤并加速開發(fā)周期。同時,設(shè)計方法學(xué)還考慮了可測試性、低功耗設(shè)計和安全性,以應(yīng)對日益復(fù)雜的應(yīng)用需求。未來,隨著人工智能和異構(gòu)集成的發(fā)展,VLSI設(shè)計方法學(xué)將繼續(xù)演進,推動集成電路向更高性能、更小尺寸和更低成本的方向前進。

如若轉(zhuǎn)載,請注明出處:http://m.fdspxw.cn/product/30.html

更新時間:2026-03-01 21:33:55